# Green mode PWM IC FA8A12N

#### 1.Overview

Datasheet

FA8A12N is a current mode type switching power supply control IC possible to drive a power MOSFET directly. Despite of a small package with 8 pins, it has a lot of functions and it is best suited for power saving at the light load and decreasing external parts. Moreover it enables to realize a reduced space and a high cost-performance power supply.

#### 2.Features

#### Low standby power

- Built-in discharge function for X-Capacitor (Reduce loss of the discharge resistor)

- · Low operating current

- (During normal operation IVccop1=450uA typ.)

- · Reduce of switching frequency at middle load

- · Burst mode at light load

- · Built-in 500V high voltage startup circuit.

#### Various Protection

- Two-stages Over Load Protection. (Delay time Tdlyolp=200msec typ.)

- Built-in OLP line compensation

- · Short Circuit Protection for secondary side

- · Latch stop function by pull-up/pull-down of LAT pin.

- Over-Voltage Protection(Vthovp=25.5V typ.)

- Under-Voltage Lock-Out function(Vccoff=6.5V typ.)

- Built-in Soft-Start function(Tss=11msec typ.)

- · Built-in Minimum ON width function.

- Low EMI by Frequency diffusion function

- Drive circuit for MOSFET: -0.5A(sink)/0.5A(source)

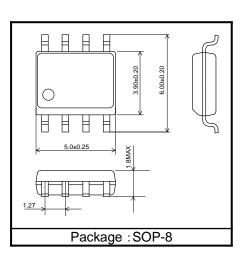

#### Line up

| Part Number | OLP Type           | Switching Frequency |

|-------------|--------------------|---------------------|

| FA8A12N     | Automatic recovery | 65kHz               |

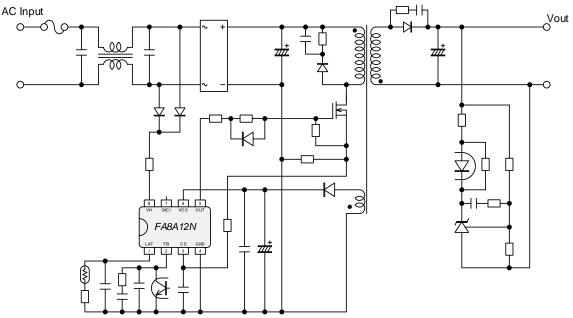

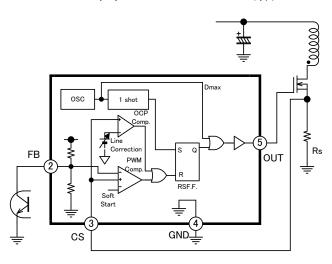

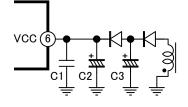

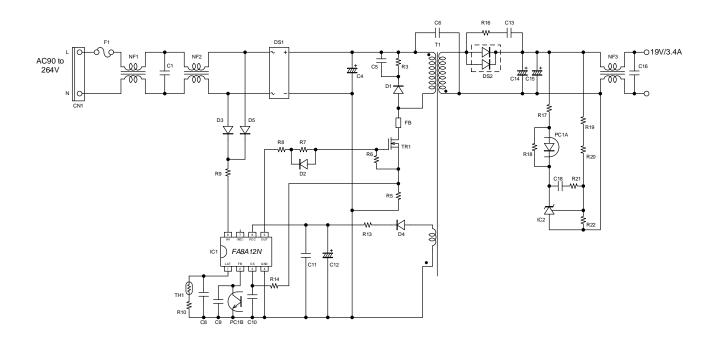

#### 3.Example of application circuit

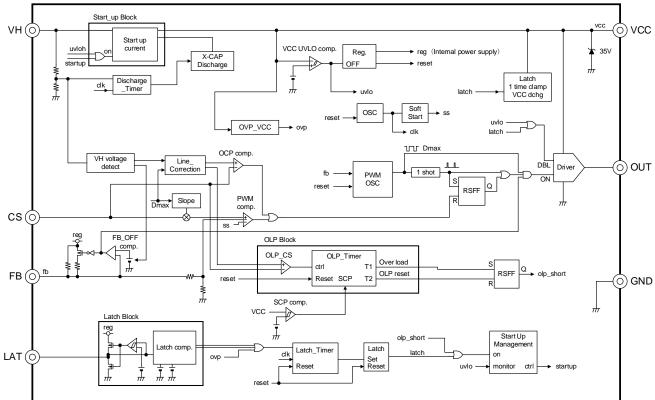

## 4.Block diagram

# FO Fuji Electric

## FA8A12N Datasheet

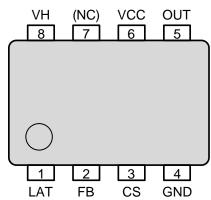

#### 5.Functional description of pins

| Pin No. | Pin Name | Pin function                                                                                                   |

|---------|----------|----------------------------------------------------------------------------------------------------------------|

| 1       | LAT      | External latch signal input *1                                                                                 |

| 2       | FB       | Feedback control signal input *1                                                                               |

| 3       | CS       | Current sense input, Over load protection(OLP)<br>Over current protection(OCP)*1                               |

| 4       | GND      | Ground                                                                                                         |

| 5       | OUT      | Output                                                                                                         |

| 6       | VCC      | Power supply, Under voltage lock out(UVLO)<br>Over voltage protection(OVP)<br>Short circuit protection (SCP)*1 |

| 7       | (NC)     | (No connection)                                                                                                |

| 8       | VH       | High voltage input<br>AC input filter capacitance(XCAP) discharge*2                                            |

Notes)

\*1. Connect capacitor between terminal pin and GND.

\*2.Connect diode and resistor between VH and the AC line.

## 6.Rating & characteristics

#### (1) Absolute maximum ratings

\*Stress exceeding absolute maximum rating may malfunction or damage the device.

\*"-" shows source and "+" shows sink in current descriptions.

|                        | Item                   | Symbol  | Value           | Unit |

|------------------------|------------------------|---------|-----------------|------|

| LAT pin voltage        |                        | Vlat    | -0.3 to 3.3     | V    |

| LAT pin current        |                        | llat    | -100 to 100     | μA   |

| FB pin voltage         |                        | Vfb     | -0.3 to 3.3     | V    |

| FB pin current         |                        | lfb     | -200 to 100     | μA   |

| CS pin voltage         |                        | Vcs     | -0.3 to 3.3     | V    |

| CS pin current         |                        | lcs     | -100 to 100     | μA   |

| OUT pin voltage        |                        | Vout    | -0.3 to VCC+0.3 | V    |

| OUT pin current        |                        | lout    | -500 to 500     | mA   |

| OUT pin peak current   | *4                     | lout_pk | -1000 to 1000   | mA   |

| VCC pin voltage        |                        | Vcc     | -0.3 to 28      | V    |

| VCC pin current *3     | At pulse voltage input | IVcc1   | -10 to 20       | mA   |

| VCC pin current 3      | At minus voltage input | IVcc2   | -0.1 to 0       | mA   |

| VH pin voltage         |                        | Vvh     | -0.3 to 500     | V    |

| VH pin current *3      |                        | lvh     | -0.1 to 10      | mA   |

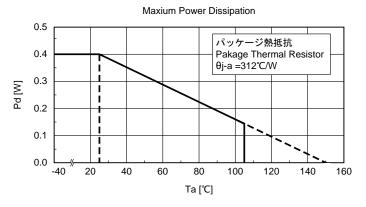

| Power dissipation(Ta=  | 25 ºC)                 | Pd      | 400             | mW   |

| Operating junction ten | perature               | Tj      | -30 to 150      | °C   |

| Storage temperature    |                        | Tstg    | -40 to 150      | °C   |

Notes)

\* 3. Please consider power supply voltage and load current well and use this IC within maximum temperature in operation. The IC may cross maximum power dissipation at normal operating condition by power supply voltage or load current within peak current absolute maximum rating value.

\*4. The period that exceeds 500mA must be 100ns or less.

#### \*Maximum dissipation curve

#### (2) Recommended operating conditions

| Item                              | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------|------|------|------|------|

| Supply voltage                    | Vcc    | 12   | 18   | 24   | V    |

| VH input voltage                  | Vvh    | 100  | -    | 400  | V    |

| Resistor connected to VH pin *5   | Rvh    | 5.6  | -    | 15   | kohm |

| Capacitor connected to VH pin *6  | Cvh    | 0    | -    | 100  | pF   |

| Capacitor connected to LAT pin    | Clat   | 100  | -    | 3300 | pF   |

| Capacitor connected to VCC pin    | CVcc   | 22   | 33   | 56   | μF   |

| Ambiance temperature in operation | Та     | -30  | -    | 105  | °C   |

Notes)

\*5. At the all wave rectification.

\*6.Verity no malfunction of XCAP discharge function occurs in case of capacitor connection.

#### (3)DC electrical characteristics

The characteristics in this section are those in conditions as follows unless otherwise specified.

The voltages described in the conditions are DC input values(not AC input values)

(Vfb = 2.0V, Vcs = 0V, Vcc= 18V, Vvh = 120V, Rlat = 100k $\Omega$ , Clat = 1000pF, Tj = 25 °C unless otherwise specified.) \* "-" shows source and "+" shows sink in current descriptions.

#### External latch-off (LAT pin)

| Item                        | Symbol     | Condition                              | Min. | Тур. | Max. | Unit |

|-----------------------------|------------|----------------------------------------|------|------|------|------|

|                             | llatsrc    | Source :<br>Vfb = 0V,<br>Vlat = 0.8V   | -50  | -40  | -30  | μA   |

| LAT output current          | llatsnk    | Sink :<br>Vfb = 0V,<br>Vlat = 1.8V     | 0.5  | 1.0  | 2.0  | μA   |

| LAT threshold voltage       | VthlatH *7 | Vlat increasing                        | 1.9  | 2.1  | 2.3  | V    |

| for latch-off               | VthlatL *8 | Vlat decreasing                        | 0.5  | 0.6  | 0.7  | V    |

| LAT resistance at latch-off | Rlatoff    | VthlatL / ( -1×llatsrc )               | 13   | 15   | 17   | kohm |

|                             | VclplatH   | Vlat increasing<br>Ilat = Source→ Sink | 1.35 | 1.50 | 1.65 | V    |

| LAT clamp voltage           | VclplatL   | Vlat decreasing<br>Ilat = Sink →Source | 0.81 | 0.90 | 0.99 | V    |

| Latch-off delay time        | Tdlylat    | Vlat > VthlatH or<br>Vlat < VthlatL    | 57   | 72   | 88   | μs   |

#### Notes)

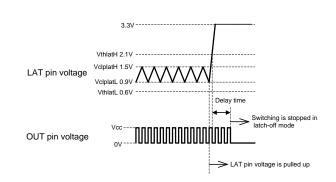

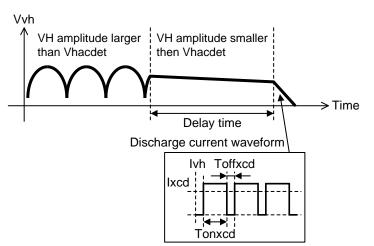

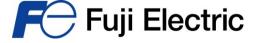

- Latch-off operation by LAT pin

- \*7. Switching is stopped in latch-off mode when LATpin is pulled up over 2.1V.

- \*8. Switching is stopped in latch-off mode when LAT pin is pulled down below 0.6V.

When LAT pin voltage becomes more than VclplatH, IC starts switching. Then, IC becomes the test mode until LAT pin voltage falls to VclplatL from VclplatH, and XCAP discharge function and the frequency modulation function do not operate. When LAT pin voltage is fixed from the outside in the range of from VclplatH to VthlatH before UVLO is released, IC operates in a test mode. However, since test mode operation is not guaranteed, please do not use it in test mode.

Larch-off operation by pulling up LAT pin voltage

LATCH operation at start-up

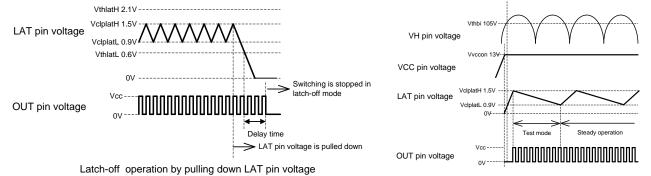

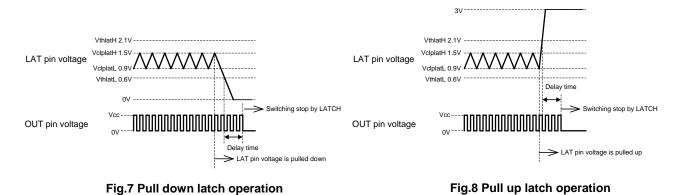

#### Soft-start function (OUT pin)

| Item                                        | Symbol | Condition                                              | Min. | Тур. | Max. | Unit |

|---------------------------------------------|--------|--------------------------------------------------------|------|------|------|------|

| Soft-start time *9                          | Tss    | Vss = 470mV<br>(Internal voltage to PWM<br>comparator) | 8.5  | 11.0 | 13.5 | ms   |

| Steady-state operation<br>start time *9 *10 | Tssend |                                                        | 14.0 | 17.0 | 20.0 | ms   |

#### Notes)

\*9. During start-up after UVLO, Over Load Protection restart.

\*10. Switching frequency modulation starts and minimunm on pulse : Tmin2 -> Tmin1 In start-up, CS pin voltage where OUT pin turns off is limited by also soft-start signal.

Soft-start operation

#### Switching oscillator (FB, OUT pin)

| Item                                    | Symbol | Condition                            | Min. | Тур. | Max. | Unit |

|-----------------------------------------|--------|--------------------------------------|------|------|------|------|

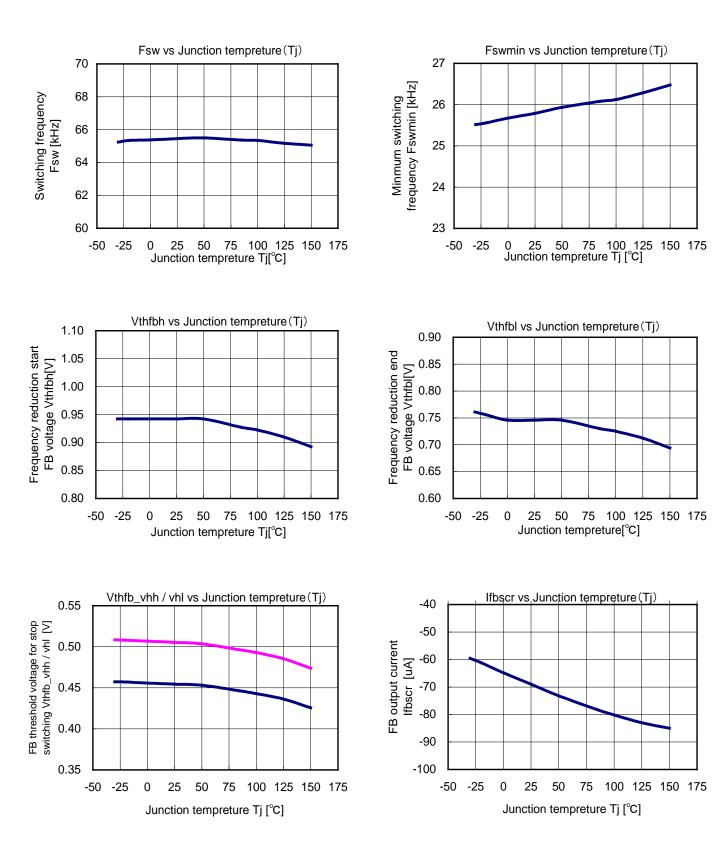

| Switching frequency                     | Fsw    | Vlat = 1.8V                          | 62   | 65   | 68   | kHz  |

| Voltage stability                       | FswdV  | Vcc = 12V to 24V,<br>Vlat = 1.8V     | -2   | -    | 2    | %    |

| Temperature stability                   | FswdT  | Vlat = 1.8V<br>Tj = -30 °C to 125 °C | -5   | -    | 5    | %    |

| Frequency modulation ratio              | Rfm    | Vfb⇒Vthfbll<br>∆Fsw / Fsw            | ±5   | ±7   | ±9   | %    |

| Frequency modulation period             | Tfm    | Vfb > Vthfbll                        | 1    | 2    | 3    | ms   |

| Frequency reduction start<br>FB voltage | Vthfbh | Vfb decreasing<br>Freq.=Fsw×0.9      | 0.8  | 0.9  | 1.0  | V    |

| Frequency reduction end<br>FB voltage   | Vthfbl | Vfb decreasing<br>Freq.=Fswmin×1.1   | 0.70 | 0.80 | 0.90 | V    |

| Minimum switching frequency             | Fswmin | Vfb = 0.7V                           | 22.5 | 25   | 27.5 | kHz  |

Notes)

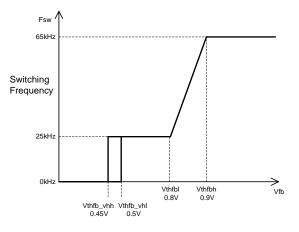

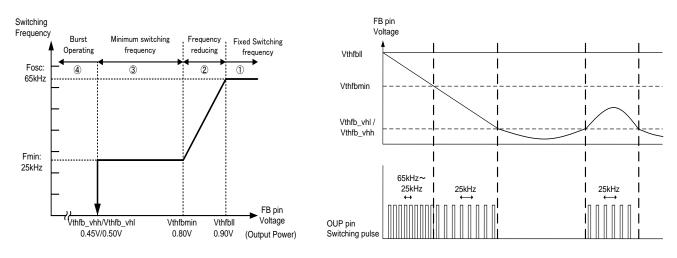

Switching Frequency vs. FB pin voltage

Switching frequency is controlled by FB pin voltage at 25kHz to 65kHz.

Switching Frequency vs. FB pin voltage

#### Pulse width modulation (FB pin)

| Item                     | Symbol    | Condition                                                                                                    | Min. | Тур. | Max. | Unit  |

|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------|------|------|------|-------|

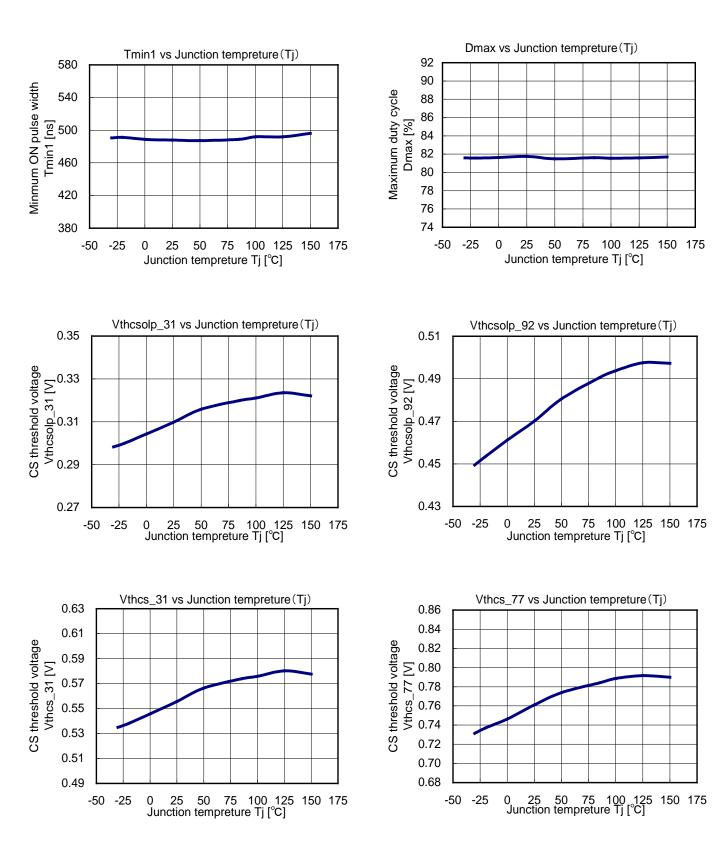

| Maximum duty cycle       | Dmax      |                                                                                                              | 73   | 83   | 93   | %     |

| Minimum duty cycle       | Dmin      | Vfb = 0V                                                                                                     | -    | -    | 0    | %     |

| FB threshold voltage for | Vthfb_vhl | Vfb decreasing<br>OUT 0% Duty<br>Vh <vthvh1< td=""><td>450</td><td>500</td><td>550</td><td>mV</td></vthvh1<> | 450  | 500  | 550  | mV    |

| stops switching          | Vthfb_vhh | Vfb decreasing<br>OUT 0% Duty<br>Vh≥Vthvh1                                                                   | 400  | 450  | 500  | mV    |

| CD nin registeres        | Rfb1      | Vfb = 0V to 0.4V                                                                                             | 40   | 60   | 80   | kΩ    |

| FB pin resistance        | Rfb2      | Vfb = 0.7V to 2.0V                                                                                           | 28.5 | 42   | 55.5 | kΩ    |

| FB output current        | lfbsrc    | Source :<br>Vfb = 0V,<br>Vlat = 1.8V                                                                         | -80  | -60  | -40  | μA    |

| Slope compensation       | Slope     |                                                                                                              | 16   | 20   | 24   | mV/µs |

|                          | Tmin1     | In steady state                                                                                              | 380  | 480  | 580  | ns    |

| Minimum ON pulse width   | Tmin2     | In soft start                                                                                                | 180  | 280  | 380  | ns    |

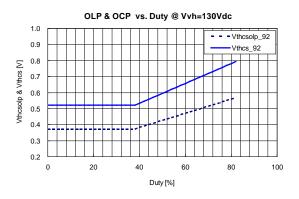

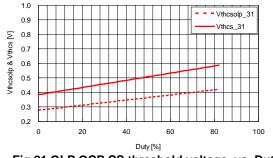

#### Over load protection (CS pin)

| Item                                          | Symbol      | Condition                                  | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|-------------|--------------------------------------------|------|------|------|------|

| CS threshold voltage for over load protection | Vthcsolp_31 | Vvh = 170Vdc<br>Fsw = 65kHz<br>Ton = 3.1µs | 0.29 | 0.31 | 0.33 | V    |

|                                               | Vthcsolp_92 | Vvh = 130Vdc<br>Fsw = 65kHz<br>Ton = 9.2µs | 0.45 | 0.47 | 0.49 | V    |

| Over load detection<br>delay time *11         | Tdlyolp     | At over load condition                     | 160  | 200  | 240  | ms   |

| Over load detection<br>Operating time         | Tolprestrt  | Vcs>Vthcsolp<br>Vvh=130Vdc<br>Ton=9.2us    | 1200 | 1500 | 1800 | ms   |

Notes)

\*11. When CS pin voltage exceeds Vthcsolp, the overload flag is set to High. Overload flag is sampled every about 0.5 ms, and fluctuates the value of the up down counter for olp based on its High / Low. If the value of the up down counter is set to 384, IC will stop in the overload mode.

#### Current sense (CS pin)

| Item                                                 | Symbol   | Condition                                                                  | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|----------|----------------------------------------------------------------------------|------|------|------|------|

| Voltage gain                                         | Avcs     | Vfb = 0.6V,<br>Vcs increasing,<br>Pulse width = Tmin1,<br>Avcs = Vfb / Vcs | 2.8  | 3.2  | 3.6  | V/V  |

| CS threshold voltage for<br>current limit protection | Vthcs_31 | Vvh = 170Vdc<br>Vfb = 3.0V<br>Fsw = 65kHz<br>Ton = 3.1µs                   | 0.38 | 0.44 | 0.50 | V    |

|                                                      | Vthcs_92 | Vvh = 130Vdc<br>Vfb = 3.0V<br>Fsw = 65kHz,<br>Ton = 9.2µs                  | 0.58 | 0.66 | 0.74 | V    |

| Current limit protection<br>delay time               | Tdlyocp  | At current limit condition                                                 | 100  | 200  | 300  | ns   |

#### Drive output (OUT pin)

| Item                   | Symbol   | Condition                 | Min. | Тур. | Max. | Unit |

|------------------------|----------|---------------------------|------|------|------|------|

| Output low voltage     | Voutl    | Vfb = 0V,<br>lout = 100mA | 0.5  | 1.0  | 2.0  | V    |

| Output high voltage    | Vouth    | lout = -100mA             | 14.5 | 16.0 | 18.0 | V    |

| Output voltage at UVLO | Voutuvlo | Vcc = 6V,<br>lout = 5mA   | 50   | 100  | 300  | mV   |

| Rise time              | Trise    | Vcc = 24V,<br>CL = 1nF    | 40   | 80   | 120  | ns   |

| Fall time              | Tfall    | Vcc = 24V,<br>CL = 1nF    | 20   | 40   | 70   | ns   |

#### VCC section (VCC pin)

| Item                                         | Symbol  | Condition                      | Min. | Тур. | Max. | Unit |

|----------------------------------------------|---------|--------------------------------|------|------|------|------|

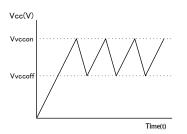

| UVLO release voltage                         | Vccon   | Vcc increasing                 | 12   | 13   | 14   | V    |

| UVLO voltage                                 | Vccoff  | Vcc decreasing                 | 6.0  | 6.5  | 7.0  | V    |

| UVLO hysteresis                              | Vcchys  | Vccon - Vccoff                 | 5.0  | 6.5  | 8.0  | V    |

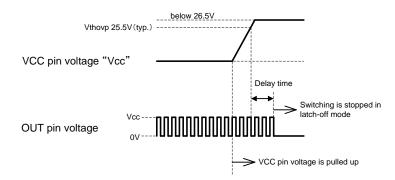

| Over voltage protection<br>threshold voltage | Vthovp  | Vcc increasing                 | 24.5 | 25.5 | 26.5 | V    |

| Over voltage protection<br>delay time        | Tdlyovp | Vcc › Vthovp                   | 57   | 72   | 88   | μs   |

| SCP threshold voltage                        | Vthscp  | Vcs>Vthcsolp<br>Vcc decreasing | 9    | 10   | 11   | V    |

|                                              | Vcclhh  | Vvh = 120V,<br>1 tme clamp     | 10.5 | 11.5 | 12.5 | V    |

| VCC voltage at latch-off                     | Vcclh   | Vvh = 120V,<br>Vcc upper level | 8    | 9    | 10   | V    |

|                                              | Vccll   | Vvh = 120V,<br>Vcc lower level | 7    | 8    | 9    | V    |

| VCC voltage at OLP                           | Vcclph  | Vcc upper level                | 11.5 | 12.5 | 13.5 | V    |

| VCC voltage at OLP                           | Vcclpl  | Vcc lower level                | 10.5 | 11.5 | 12.5 | V    |

Notes)

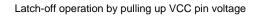

OVP operation by VCC pin

Switching is stopped in latch-off mode when VCC pin is pulled up over Vthovp.

Schematic view of operation at the time of over load detection operating time of VCC pin and latch-off mode.

#### VCC clamp description

#### Power supply current (VCC pin)

| Item                                              | Symbol    | Condition                                              | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|-----------|--------------------------------------------------------|------|------|------|------|

|                                                   | IVccop1   | OUT no load,<br>OUT max. Duty                          | 0.20 | 0.45 | 0.90 | mA   |

| Supply current in operating                       | IVccop2   | Vfb = 0V,<br>Vcc = 12V,<br>OUT no load,<br>OUT 0% Duty | 0.10 | 0.25 | 0.45 | mA   |

| Supply current at stopped by over load protection | IVccolp   | Vfb = 0V,<br>Vcc = 13.5V,<br>Vvh = 0V                  | 0.10 | 0.20 | 0.45 | mA   |

| Supply current at latch-off                       | lvcclatcl | Vfb = 0V,<br>Vcc = 15V<br>Vvh =0V                      | 3.5  | 6.0  | 10.0 | mA   |

|                                                   | lvcclat   | Vfb = 0V,<br>Vcc = 10V,<br>Vvh =0V                     | 0.30 | 0.60 | 1.00 | mA   |

## High-voltage Input section (VCC, VH pin)

| Item                                         | Symbol | Condition                                      | Min. | Тур. | Max. | Unit |

|----------------------------------------------|--------|------------------------------------------------|------|------|------|------|

| VH input current                             | lvhrun | Vfb = 0V,<br>Vvh = 450V                        | 3    | 5    | 20   | μA   |

|                                              | lvhstb | Vfb = 0V,<br>Vcc = 0V,<br>Vvh = 120V           | 0.4  | 0.8  | 1.6  | mA   |

|                                              |        | Vfb = 0V,<br>Vcc = 6V  to  11V<br>Vvh = 120Vdc | 2.0  | 3.0  | 4.0  | mA   |

| Charge current for VCC                       | lpre   | Vfb = 0V,<br>Vcc = 11V,<br>Vvh = 120V          | -3.7 | -2.7 | -1.7 | mA   |

| VH threshold voltage of<br>changing Vthfb    | Vthvh1 | Vvh incresing                                  | 200  | 235  | 270  | Vdc  |

| VH threshold voltage of<br>changing Vthcsolp | Vthvh2 | Vvh incresing                                  | 140  | 155  | 170  | Vdc  |

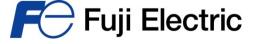

#### XCAP discharge circuit (VH pin)

| Item                                       | Symbol   | Condition                         | Min. | Тур. | Max. | Unit |

|--------------------------------------------|----------|-----------------------------------|------|------|------|------|

| Average discharge current<br>for XCAP      | Ixcd     | In XCAP discharge                 | 1    | 2    | 4    | mA   |

| ON-time for XCAP<br>discharge current      | Tonxcd   | In XCAP discharge                 | 1.2  | 1.5  | 1.8  | ms   |

| OFF-time for XCAP<br>discharge current     | Toffxcd  | In XCAP discharge                 | 0.4  | 0.5  | 0.6  | ms   |

| VH Ampulitud ensured                       |          | Vvh=67 to 124V                    | 50   | -    | -    | V    |

| AC detection                               |          | Vvh=236 to 358V                   | 75   | -    | -    | V    |

| VH Ampulitud garenteed<br>AC non detection | Vhnacdet | Vvh=67 to 97V<br>Vvh=281V to 358V | -    | -    | 5    | V    |

| Delay time for AC detection                | Tacdet   |                                   | 40   | 56   | 72   | ms   |

#### Notes)

When AC input is stopped and change of VH pin voltage is not detected, it goes into XCAP electric discharge operation after AC detection delay time is over.

An operating waveform in XCAP discharge function

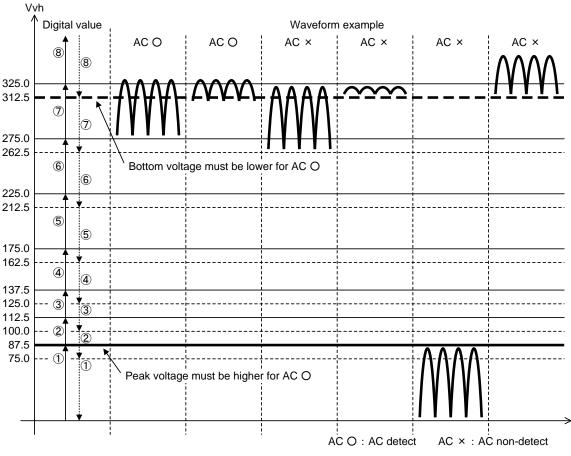

VH pin voltage conditions, as for, AC detection carries out a normal operation are that a peak voltage is higher than 87.5V(design value) and a bottom voltage is lower than 312.5V(design value).

VH pin voltage is converted to one of 8 digital values with hysteresis characteristics. At least one increment of the digital value in each AC detection delay time Tacdet is required for judging AC supplies.

Explanation of AC detection method

## Fuji Electric FA8A12N Datasheet

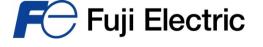

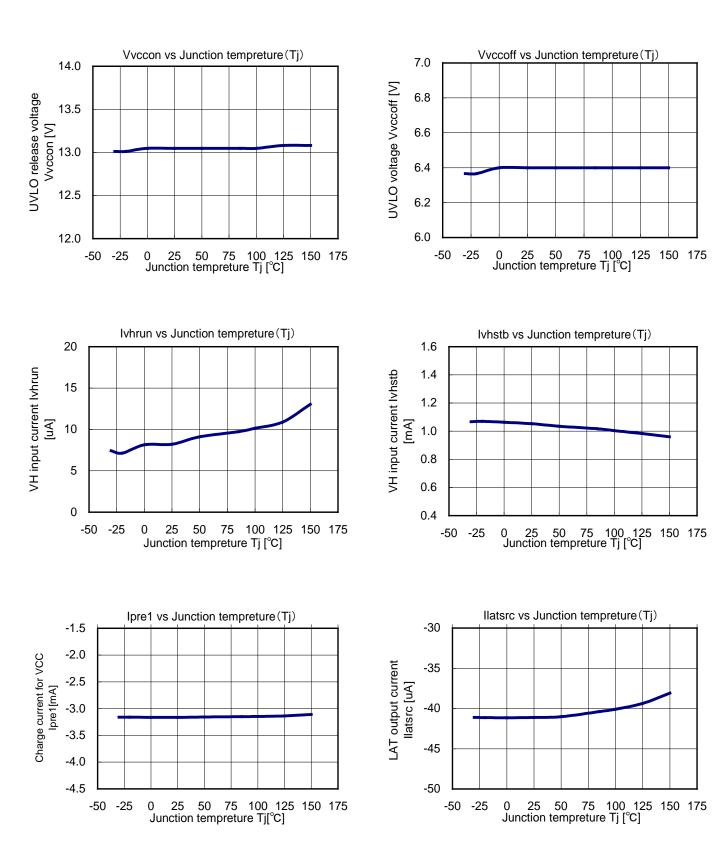

## 7.Characteristic Curve (DC Characteristics)

- •Unless otherwise specified : Vcc=18V, Vvh = 120V ,Vfb = 2.0V, Vcs = 0V, Rlat = 100kΩ, Clat = 1000pF, Tj = 25°C

- "+" shows sink and "-" shows source in current prescription.

•Data listed here shows the typical characteristics of an IC and does not guarantee the characteristics.

#### 8.Description of the function

(The values in the following description are typical values unless otherwise specified.)

#### (1) PWM control

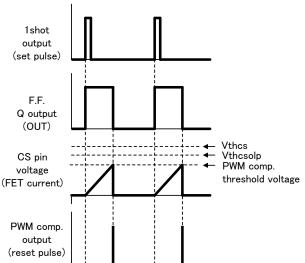

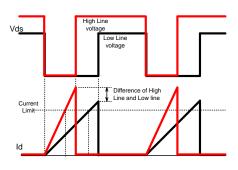

FA8A12N operates by current mode control. The circuit block of current mode is shown in Fig.1, and the timing chart is shown in Fig.2. The trigger signal which determines the switching frequency made with the oscillator is inputted into a RS flip-flop (RS F.F.) as a set signal through a one shot (one shot) circuit. When a set signal is inputted into RS flip-flop, the output of RS flip-flop is set to High and OUT pin voltage also be set to High. On the other hand, PWM comparator (PWM comp.) detects the current of MOSFET as a voltage value of Rs and if the detected voltage reaches threshold voltage, PWM comp will output a reset signal. When a reset signal is inputted to RS flip-flop, the output of RS flip-flop is set to Low, and OUT pin voltage is also set to Low. Thus, ON pulse width of OUT pin is controlled by threshold voltage of a PWM comparator. The output is controlled by changing the threshold voltage of this PWM comp. Comparing FB pin voltage and soft start voltage are inputted into the PWM comp. Moreover, CS pin voltage and soft start voltage of the Line Correction block are inputted into the OCP comp., and the maximum MOSFET current is limited. The oscillator outputs pulses for determining the maximum duty cycle. Using these pulses, the maximum duty cycle has been set to 83% (typ).

Fig1. Current mode basic operation circuit block

Fig2. Current mode basic operation timing chart

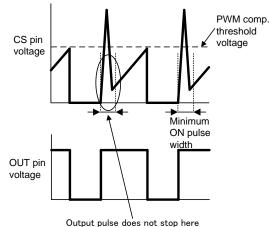

#### (2) Minimum ON pulse width function

When the MOSFET is turned on, a surge current is generated due to discharge corresponding to the capacitance of the main circuit and gate drive current. If this surge current reaches the CS pin threshold voltage, normal pulses may not be generated from the OUT pin. To avoid this phenomenon, a Minimum ON width of OUT pin output is set within the one-shot circuit block of the IC.

If a trigger signal having the switching frequency is input from the oscillator, a pulse having a specific width is output as a RS (F.F.) set signal. Since the set signal has priority over the input signal of the RS (F.F.), the output of the RS (F.F.) is not reversed while the set signal from the one-shot circuit is being input, even if a reset signal is input from the PWM comparator.(See Fig.1)

As a result, the input to the CS pin is kept invalid for the specified period of time immediately after the output pulse is generated from the OUT pin (minimum ON width), and made not to respond to the surge current at turn-on. (See Fig.3)

because of this minimum ON pulse width

#### Fig.3. Minimum ON pulse

#### (3) Reduce of switching frequency function

FA8A12N equipped with the function to reduce the switching frequency according to the load. The switching frequency in the normal operation mode is set to 65kHz within the IC. To minimize the loss at light load, switching frequency is reduced automatically in proportion to the FB pin voltage. (Fig.4) When FB voltage decreased to 0.8V of Vthfbmin, Switching frequency is set to 25kHz of the minimum frequency. In addition, when FB voltages decrease under FB threshold voltage for stop switching, the IC operates in burst mode. (Fig.5)

Fig4. Switching frequency - FB voltage (Output power)

#### (4)Two stage Over load protection

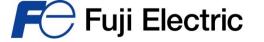

FA8A12N incorporates overload protection of auto recovery type. Fig. 6 shows the timing chart of the overload protection operation. The overload protection circuit detects overload at the CS pin voltage, and if the state of overload continues for over the delay time (Tdlyolp=200msec), it stops switching. When the over load stopping time (Tolprestrt=1500msec) had elapsed, the IC re-start switching operation. This auto recovery repeats until over load condition is reset.

The CS pin overload protection threshold voltage is set at a lower voltage than the current limit threshold voltage (2 stage OLP). Therefore peak output power which depends on the current limit is larger than overload and peak power can output within a delay time of overload protection (200ms) keeping the output voltage. This is best suited for applications where the peak current is needed.

For the overload delay timer, an up/down counter is used, and the same period is required for count down to clear the count-up. If, therefore, the overload period (t1) continues longer than the steady operation period (t2), the count-up will be accumulated and the overload protection will operate in a shorter time than the overload delay time (t3). Attention must be paid for such operation as to repeat the overload and rated load.

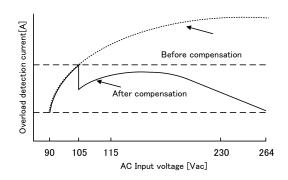

Generally the overload output changes depending on the AC input voltage. This IC changes the CS pin overload threshold voltage and the CS pin current limit threshold according to the AC input voltage, thereby compensating the dependency on the input voltage. (For the details, see P23 (III) Overload detection and overcurrent limit)

Fig6.Two stage over load protection timing chart (Auto recovery)

#### (5) Short Circuit Protection (SCP)

FA8A12N incorporates a secondary-side output short-circuit protection function (SCP). If secondary-side output is shorted, the over load detects at the CS pin. In addition, VCC voltage drops because auxiliary winding voltage almost zero. IC stops switching operation immediately when CS pin voltage exceeds overload detection voltage and Vcc drops below Vthscp (11V typ.). FA8A12N restart switching operation after 1500ms and repeats it until short circuit condition is removed.

#### (6) Latch function by external signal

LAT pin incorporates 2 types of latched shutdown function; pull-up and pull-down. Figs.7 and 8 show latch operations. If the LAT pin voltage is pulled up higher than the threshold voltage VthlatH=2.1V or pulled down lower than VthlatL=0.6V for over the delay time (Tdlylatch: 65us), switching will be stopped in latch mode. (For resetting the latch stop, see P.19-(13))

#### (7) Soft-start function

When switching is started, ON width of the OUT pin gradually is widened, thus preventing Vds surge voltage of power MOSFET when starting. The soft-start period is fixed inside the IC.

Fig9.Soft-start function

# Fuji Electric

## FA8A12N Datasheet

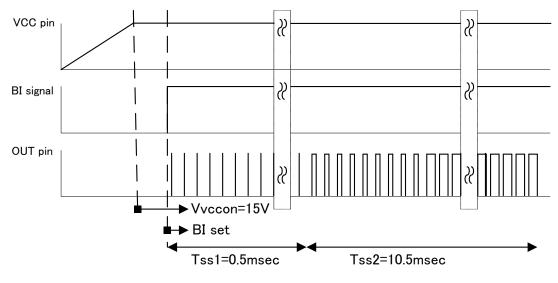

## (8) X-Capacitor discharge function

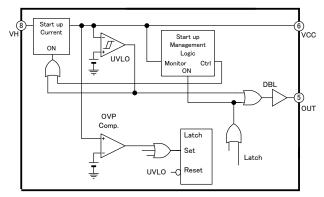

FA8A12N incorporates the function to discharge X-capacitor Cx of the AC input line filter. As shown in Fig.10 and Fig. 11, VH pin connected to the Cx at AC input with full-wave rectification and Cx is discharged via VH pin when AC line voltage is cut off. Therefore discharge resistor Rx for X-capacitor can be removed and the loss is reduced.

Recommend value of X-capacitor <=0.47uF

The demand about the electric shock of UL60950: The voltage value of the power supply input unit is need to do less than 37% of peak voltage values within 1 second after AC input voltage interception.

Fig10. VH pin discharge circuit

Fig11.X-Capacitor discharge operation

#### (9) Frequency diffusion (Spread spectrum)

FA8A12N performs frequency modulation of  $\pm$  7.0 kHz for switching frequency 65 kHz. This function enables more noise energy of the switching to disperse compared to the case with fixed frequency and obtains a conduction EMI reduction effect. While the reduction effect depends on the filter parts mounted on the power supply board, effective use of this function allows the reduction of the number of the filter parts and the constants.

#### (10) Over voltage protection

FA8A12N integrates an over voltage protection circuit for monitoring the VCC pin voltage. If the VCC voltage increases and exceeds 25.5V, set the latch circuit to perform latch shutdown. Since 72 us delay time has been set to the set input of the latch circuit, the latch mode is not entered even if the VCC pin exceeds the detection voltage temporarily. (For resetting the latch stop, see P.19-(13))

#### (11) Under voltage lockout function (UVLO)

FA8A12N integrates an under voltage lockout (UVLO) function to prevent circuit malfunction that might occur when power supply voltage decreases. When the VCC voltage increases from 0V and reaches 15V, the circuit starts operating When the VCC decreases down to 6.5V, the circuit stops operating. In a state in which the UVLO is actuated to stop IC operation, the OUT pin is forcibly made to enter the Low state. The latch mode of the protection circuit is also reset.

#### (12) Cancel of Latch condition

During the latch stopping, the startup circuit repeats ON/OFF so that the VCC voltage will be kept in the range of Vcclh=9V/Vccll=8V to maintain the latch state. The latch mode can be reset by cutting off the input voltage and lowering the VCC voltage below the OFF threshold voltage (Vccoff=6.5V).

#### 9.Description of use each pin and advice for designing

#### (1) Pin No.1 (LAT pin)

#### [Function]

- (i) Performs latch-off protection by pull-down

- (ii) Performs latch-off protection by pull-up

#### [How to use]

#### (i)Latch-off protection by pull-down

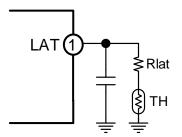

Connection method

Fig. 12 shows the connection of an over temperature protection circuit using NTC thermistor and Fig. 13 shows the connection of a protection circuit using external signal.

· Operation

If the LAT pin voltage is pulled down below the latch off threshold voltage VthlatL=0.6V for over 72us,switching is stopped in latch mode. The latch mode can be reset by cutting off the input voltage and lowering the VCC voltage below the OFF threshold voltage (Vccoff=6.5V). During the latch stopping, the startup circuit repeats ON/OFF so that the VCC voltage will be kept in the range of Vcclh=9V/Vccll=8V to maintain the latch state.

#### Advice for designing

(1)Over temperature protection

NTC thermistor TH connects to the LAT pin.Since the LAT pin source current is Ilatsrc= $40\mu$ A, select TH1 whose resistor Rth satisfies the following expression at the desired over temperature protection. If temperature setting for overheat protection is not feasible with TH1 only, connect an additional resistor (Rlat) in series for adjustment.

TH@LAT + Rlat ≤0.6V / 40uA ≈15kΩ

Fig.12 Over temperature circuit

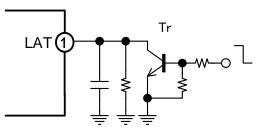

(2)Latch stop function by an external signal NPN transistor Tr is connected to LAT pin . The polarity of the input signal must be such that the level will go high at an error.

Fig.13 Latch circuit by external signal

#### (ii)Latch-off protection by pull-up

- Connection method

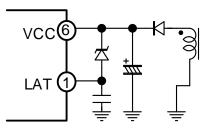

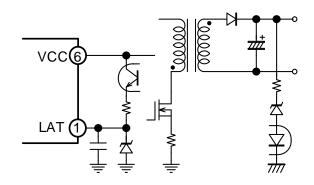

Figs. 14 and 15 show the connection examples of the over voltage protection circuit.

- Operation

If the LAT pin voltage is pulled up over the latch stop threshold voltage VthlatH=2.1V for over 72us, switching is stopped in latch mode.The latch mode can be reset by cutting off the input voltage and lowering the VCC voltage below the OFF threshold voltage (Vccoff=6.5V). During the latch stopping, the startup circuit repeats ON/OFF so that the VCC voltage will be kept in the range of Vcclh=9V/Vccll=8V to maintain the latch state.

Fig.14 Over voltage circuit (1)

Fig.15 Over voltage circuit (2)

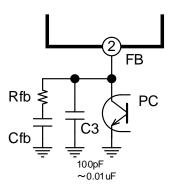

#### (2) Pin No.2 (FB pin) [Function]

(i)Input feedback signals from the secondary side.(ii)Reduce switching frequency(iii)Burst mode operation

#### [How to use]

#### (i)Input feedback signals

Connection method

Connect the optocoupler corrector to this pin will allow regulation. At the same time, to prevent generation of noise, connect a capacitor in parallel to the optocoupler (Fig.16)

Operation

FB pin is biased from the IC internal power supply via the resistance. The FB pin voltage is level-shifted and input into the current comparator to provide the threshold voltage of the MOSFET current signals to be detected with the CS pin.

#### (ii)Frequency reduction

- Connection method

- The same as the input feedback signal in (i).

- $\cdot$  Operation

The switching frequency in the normal operation mode is set to 65kHz within the IC. To minimize the loss of power in the standby state, this IC is equipped with a function of automatically decreasing the switching frequency under light load. The minimum switching frequency is 25kHz.(P.20\_Fig.4)

#### (iii)Burst operation

- Connection method

- The same as the input feedback signal in (i). Operation

At the light load, the FB pin voltage decreases. If the voltage becomes lower than the threshold of Vthfb, the switching is stopped, and if it becomes higher, the switching is restarted. By repeating this operation, the burst operation is realized (see P.16 Fig. 5).

#### Advice for designing

Fig.17 shows the circuit configuration of the FB pin. A photo-coupler PC is connected as a feedback circuit that monitors the output voltage and performs PWM control. The FB pin provides threshold voltage of the current comparator. If noise is added to the pin, output pulse fluctuation may result. To prevent generation of noise, a capacitor having the capacitance of approximately 100pF to  $0.01\mu$ F is connected for use as shown in.

Since the capacitor connected to the FB pin not only prevents noise but also affects response, etc., optimum value should be selected with consideration of noise and response.

In addition, adjustment range spreads out by adding Rfb and Cfb between FB pin and GND, and stability behaviors. Therefore, We recommend that you connect Rfb and Cfb.(Rfb : several kohm ~ several tens of kohm Cfb : several tens of nF)

Fig.16 FB pin circuit

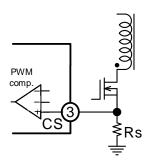

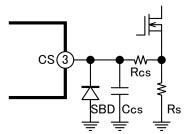

#### (3) Pin No.3 (CS pin) [Function]

- (i) Detects of the MOSFET current.

- (ii) Preventing malfunction with the minimum ON width function

- (iii) Detects of over load condition and current limits

## [How to use]

## (i)Current detection

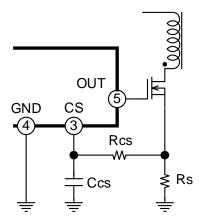

Connection method Connect a current detecting resistor Rs between the MOSFET source pin and the GND. The current signals of the MOSFET generated in the resistor are input (Fig.17).

Operation

The current signals of the MOSFET input to the CS pin is then input to the current comparator, and if it reaches

the threshold voltage determined by the FB pin, the MOSFET is turned off. This FB pin voltage fluctuates due to the feedback circuit from the output voltage to control the MOSFET current.

Fig.17 CS pin filter

#### (ii) Minimum ON width function

Connection method Same as current detection and current limits in (i)

#### · Operation

To prevent malfunction due to surge voltage when MOSFET turns on, the IC has a Minimum ON width. During this period, the input of the CS pin becomes invalid and no response is made to the surge current.

#### Advice for designing

For the CS pin, the lowest ON width is set, and the malfunction due to surge current when the power MOSFET turns on is relatively difficult to occur. But if the surge current generated when it turns on is large or when external noise is applied, the malfunction may be caused. In such a case, CR filter Ccs, Ros should be added to the CS pin as shown in Fig.18. The CR filter should be determined based on the cutoff frequency and time constant.

The cutoff frequency can be sought as follows. Fc=1 ( $2x\pi x$  Ccs x Rcs)

This frequency should be a large value against the IC operation frequency 65kHz. The CR time constant should be approximately 500nsec or lower. It should be noted that if the capacity of Ccs becomes large, the delay element will become large and the overload detection value will fluctuate.

Reference value: Rcs=1kΩ Ccs=100pF~470pF

The capacitor Ccs should be connects as near as possible to the IC to suppress the noise effectively.

Fig.18 CS pin filter

## (iii) Overload detection and overcurrent limit

· Connection method

Same as for current detection and current limit in (i). Operation

If the CS pin voltage reaches the overload threshold voltage for over 860ms, the IC detects overload and stops switching in latch mode. To limit the peak current of the MOSFET, CS pin voltage is input to OCP\_CS comparator. The peak current is limited below the value

determined by the threshold and current sense resistor.

### Advice for designing

Due to the propagation delay of OLP circuit or current limiting circuit, overshot is appear on the primary current and it varies depending on the input voltage. (Fig.19)

In this IC, the overload and current limiting threshold are compensated according to the duty cycle. As the result, dependency of overload output and peak power output to the AC line voltage are improved. (Fig.20).

The followings shows a design example of current sense resistor Rs.

At minimum AC line voltage, primary current becomes maximum. The ILp at Vin(min) is calculated approximately by the following equation.

D : Duty , Vin : Input voltage (rms)

Np : primary winding(turn) , Ns : secondary winding(turn) Vo: Output voltage , Po : Output power ,  $\eta$  : Efficiency Fsw : Switching frequency

Lp : Transformer primary side inductance  $N_{n}$

$$D = \frac{\frac{NP}{Ns} \times Vo}{\sqrt{2} \times Vin + \frac{Np}{Ns} \times Vo}$$

$$ILp = \frac{Po}{\sqrt{2} \times Vin \times D \times \eta} + \frac{\sqrt{2} \times Vin \times D}{2 \times Lp \times Fsw}$$

$$\label{eq:stample} \begin{split} & \text{Example}) \\ & \text{Vin=85V,Np=28T,Ns=5T,Lp=340uH,Fsw=65kHz,} \\ & \eta \text{=}0.9, \\ & \text{Vo=19V,Po=100W}(\text{Overload detection power}) \\ & \text{If} \end{split}$$

$$D = \frac{\frac{28}{5} \times 19}{\sqrt{2} \times 85 + \frac{28}{5} \times 19} = 0.47$$

$$ILp = \frac{100}{\sqrt{2} \times 85 \times 0.47 \times 0.9} + \frac{\sqrt{2} \times 85 \times 0.47}{2 \times 340u \times 65k} = 3.245A$$

Since D=0.47,Vthcsolp=0.41V from Fig.21

Rs = |Vthcsolp/ILp = 0.41/3.245 = 0.126

Therefore  $0.13\Omega$  is selected for Rs. However output current at overload is slightly larger than calculated value because of the delay at gate drive etc. Therefore check in actual circuit before final decision. Overload current at high line voltage can be adjusted by CS pin CR filter.

Fig.19 Overload detection level on input voltage (1)

Fig.20 Overload detection level on input voltage (2)

OLP & OCP vs. Duty @ Vvh=170Vdc

Fig.21 OLP,OCP CS threshold voltage vs. Duty

### (4) Pin No.4 (GND pin)

#### [Function]

Pin No. 4 serves as the basis of the voltage of each part of the IC.

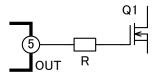

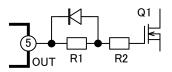

#### (5) Pin No.5 (OUT pin)

#### [Function]

Drives the MOSFET

#### [How to use]

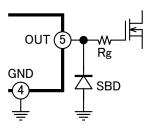

- Connection method Connect pin No.5 to the MOSFET gate through resistor

- (Fig.23,Fig.24,Fig.25)

- Operation While the MOSFET remains ON, it is in high state, and VCC voltage is output.While the MOSFET remains OFF, It is in low state, and 0 voltage is output.

#### Advice for designing

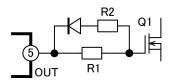

Between the gate pin of MOSFET and OUT pin of IC, resistor is generally inserted to adjust the switching speed and to prevent the parasitic oscillation at gate pin.(Fig. 22).In such a case, it may be desirable to independently determine the driving current when MOSFET is turned on or off. If so, connect the gate drive circuit in Fig.24 or Fig.25 between the gate pin of MOSFET and OUT pin of IC. In case of Fig.24, the current is limited by R1+R2 when on or by R2 alone when off. In case of Fig.25, the current is limited by R1 alone when on or it is limited by the parallel resistance of R1 and R2 when off.

Fig.22 OUT pin drive circuit (1)

Fig.23 OUT pin drive circuit (2)

Fig.24 OUT pin drive circuit (3)

## (6) Pin No.6 (VCC pin)

#### [Function]

- (i) Supplying the power of IC

- (ii) Preventing malfunction by detecting low voltage

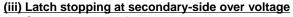

- (iii) Latch stopping at secondary-side over voltage

- (iv)Short detection for secondary side

### [How to use]

(i) Supplying power of IC

· Connection method

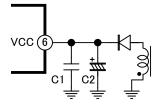

Generally, the auxiliary winding voltage provided in the transformer is rectified/smoothed and connected. (Fig.25). Or DC power from outside is connected.

· Operation

If AC input voltage is applied, the capacitor of VCC is charged by the current supplied from the start-up circuit and the voltage increases. When the VCC reaches the ON threshold voltage, the IC starts operating. In the steady-state, the IC operates by means of the voltage supplied from the auxiliary winding.

Fig.25 VCC pin circuit

#### Advice for designing

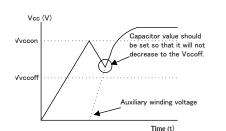

Since large current is fed to the VCC pin when the MOSFET is driven, relatively large noise tends to be generated. In addition, noise is also generated from the current supplied by the auxiliary winding. If this noise is large, malfunction of the IC may result. To minimize the noise that is generated at the VCC pin, add a bypass capacitor C2 (0.1 µF or higher) adjacent to the VCC pin of the IC, between VCC and the GND, as shown in Fig.26, in addition to the electrolytic capacitor.Just after the IC starts, the VCC pin voltage decreases until the voltage of the auxiliary winding rises enough. (Fig.26) The capacitor C2 connected to the VCC pin should be determined so that the voltage will not decrease to the OFF threshold voltage in the meantime.Specifically, to select the VCC pin capacitor so that the lower limit of the VCC pin voltage will be 6.5V or more is recommended. If the capacitor of the VCC pin is too small, VCC voltage repeats up/down operation between ON and OFF threshold voltage, and consequently the power supply cannot be turned on. (Fig.27)

#### Fig.26 VCC pin voltage at start-up

## Fig.27 VCC pin voltage at start-up (When VCC capacitor is too small)

#### (ii) Preventing malfunction by detecting low voltage

- Connection method

- Same as (1)

- Operation

To prevent circuit malfunction when supply voltage decreases, a circuit to prevent malfunction at low voltage is incorporated. When the VCC supply voltage decreases, the IC stops its operation at Vccoff=6.5V.When the IC stops operating after the circuit to prevent malfunction at low voltage operates, the OUT pin is forcefully put in Low state.The latch mode of the protection circuit will also be reset.

#### Advice for designing

It may be desirable to increase the capacitor connected to the VCC pin to prevent the VCC pin voltage from becoming lower than the off threshold voltage due to step load change, etc. after the power supply starts. If, however, the capacitor value of the VCC pin is made large, the startup time will increase. In such a case, both can be achieved by means of the circuit shown in Fig. 28. The startup time can be shortened by smaller C2, and the hold time of VCC can be made longer by C3.

Connection method Same as (1)

#### · Operation

An overvoltage protection circuit to monitor VCC voltage is incorporated. (Fig.29). If the VCC voltage rises and exceeds the 25.5V reference voltage of the OVP comparator for over the delay time of 72us, IC will stops in latch mode. Due to the delay time, OVP does not operate in momentary overvoltage such as noise.During the latch stopping, the start-up circuit repeats ON and OFF so that the VCC voltage will be kept in the range of Vcclh=9V/Vccll=8V to maintain the latch state. The latch mode can be reset by cutting off the input voltage and lowering the VCC voltage below the OFF thresholdvoltage (6.5V).

Fig.29 Over voltage circuit block

#### Advice for designing

The recommended supplied voltage range is 12 V to 24 V. When the load is light, the VCC pin voltage decreases, whereas when the load is heavy, the voltage increases, thus deviating from the power supply voltage range. In such cases, change the resistor (or inductor) between the VCC pin and the diode to adjust the voltage. (Fig.30) Also, by adding beads core at the foot of the resistor, voltage fluctuation may be suppressed. If the above methods do not work, it is recommended to change the secondary winding and the auxiliary winding of the transformer to bifilar winding.

Fig.30 VCC pin circuit

Fig.28 VCC pin circuit

## Innovating Energy Technology

#### (iv)Short detection for secondary side

- Connection method Same as (1)

- · Operation

If output of PSU is shorted, CS pin voltage exceeds the OLP detection level. In addition, Vcc voltage drops because auxiliary winding voltage is almost zero. IC stops switching operation immediately when CS pin voltage exceeds overload detection voltage and Vcc drops below Vthshort (10V typ.).As in the case of overload, FA8A12N restart switching operation after 1400ms and repeats it until short circuit condition is removed. The delay time of short circuit protection operates is dependent on the capacitor of VCC pin, and the VCC pin voltage value. If VCC pin voltage does not drop until Vthscp=10V within 70 msec, overcurrent protection operate.

#### (7) Pin No.7 (N.C.)

Since this pin is placed adjacent to the high-voltage pin, it is not connected to inside the IC.

#### (8) Pin No.8 (VH pin)

#### [Function]

(i)Supplies start-up current

(ii)Discharging the X capacitor when AC input is cut off

#### [How to use]

(i) Supplies start-up current

Connection method

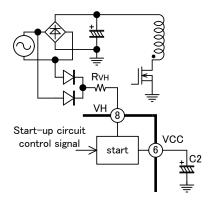

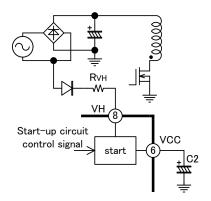

VH pin is connected to the AC line with full wave rectification via the start-up resistance of  $5.6k\text{-}15k\Omega$  and diodes. (Fig.31)

#### (Caution 1)

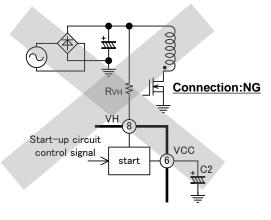

The connection shown in Fig.33 is not recommended. VH pin connected to AC line with half wave rectification and X-capacitor discharge function operates only for the half cycle of AC line voltage.

#### (Caution 2)

The VH pin cannot be connected from DC input after the AC input voltage is rectified / smoothed. X-Capacitor discharge function does not operate properly and IC may be overheated and damaged. (Fig.33)

#### (Caution 3)

If a capacitor is connected between VH pin and GND as a measure against surging of the AC input line, it should be of 100pF or lower. If a capacitor of 100pF or higher isconnected, the discharging function of the X capacitor will malfunction.

#### · Operation

This IC incorporates a start-up circuit of 500V. If AC power is input, the capacitor C2 connected to the VCC pin will be charged by the current supplied from the start-up circuit and the voltage will increase. When the VCC pin voltage reaches the on threshold voltage, the ICwill start operating. After the IC operates, the start-up circuit will be put in the cutoff state, and the VH pin current will be reduced to several tens of uA.

Fig.31 VH pin circuit (1)

Fig.32 VH pin circuit (2)

Fig.33 VH pin circuit (3)

## (ii) Discharging function of X capacitor at AC input cutoff

Connection method Same as the how to use (i).

· Operation

The AC input voltage is monitored by the VH pin, and when the AC input is cut off, the discharging function of the X capacitor will operate after 56ms of delay time. The function discharges the X-capacitor repeating ON and OFF state; ON state is for 1.5ms with average current of 2mA and OFF state is for 0.5ms.

#### (9)Other advice on designing

## (1) Preventing malfunction due to negative voltage of the pin

If large negative voltage is applied to each pin of the IC, the parasitic devices within the IC may be operated, thus causing malfunction. Confirm that the voltage of -0.3 V or less is not applied to each pin.

The vibration of the voltage generated after the MOSFET is turned-off may be applied to the OUT pin through the parasitic capacitance, resulting in a case in which negative voltage is applied to the OUT pin. In addition, negative voltage may be applied to the IS pin due to the vibration of surge current generated at the turn-on of the MOSFET.

In such cases, connect a Schottky diode between each pin and the GND. The forward voltage of the Schottky diode can suppress the negative voltage at each pin. In this case, use a Schottky diode whose forward voltage is low. Fig. 34

and Fig.35 are typical connection diagram where a Schottky diode is connected to the OUT pin.

#### (2) Loss calulation

To use the IC within its rating, it is necessary to confirm the loss of the IC. However, since it is difficult to measure the loss directly, the method of confirming the loss by calculation is shown below.

VH pin is defined as Vvh, the current fed to the VH pin during operation as Ivhrun, power supply voltage as Vcc, supply current as IVccop1, gate input charge of the MOSFET to be used as Qg, and switching frequency as Fsw, the total loss Pd of the IC can be calculated using the following formula.

$Pd \approx Vvcc \times (Ivccop1 + Qg \times Fsw) + Vvh \times Ivhrun$

A rough value can be found using the above formula, but note that Pd is slightly larger than the actual loss value. Also note that each specific characteristic value has temperature characteristics or variation.

#### Example:

When the VH pin is connected to a Full-wave rectification waveform with AC 100 V input, the average voltage to be applied to the VH pin is approximately 90 V. In this state, assume that Vcc = 15 V, Qg = 80 nC, and fsw = 65 kHz (when Tj = 25°C). Since IVHrun = 5  $\mu$ A and Iccop1 = 0.45mA from the specifications, the standard IC loss can be calculated as follows:

Pd≈15V×(0.45mA+80nC×65kHz)+90V×5uA≈85.2mW

Fig.34 inhibit OUT pin from minus voltage

Fig.35 inhibit CS pin from minus voltage

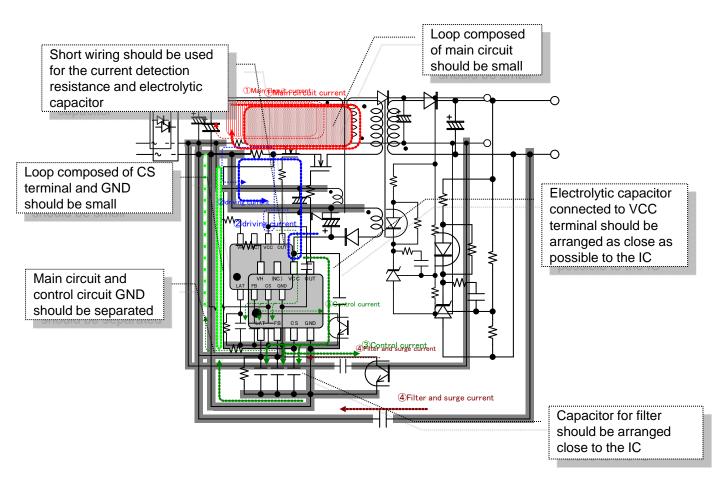

## 11.Precautions for pattern design

In the switching power supply, large pulse current flows in the GND wiring and surge voltage (noise) is generated. The noise may causes malfunction of the IC. (unstable voltage, unstable waveform, abnormal latch stop, etc.) Malfunction may also caused by injected surge voltage/current such as lighting surge test, AC line surge test and electrostatic discharge test. Please design the PCB layout and trace with consideration of the followings to prevent the malfunction.

#### Current path in switching power

- (1)Main circuit current which flows from input smoothing capacitor to transformer primary winding, MOSFET and current sense resistor.

- (2) Current which flows from auxiliary winding to VCC capacitor.

- (3) Driving current which flows from IC to the MOSFET

- (4) Control circuit current around the IC such as feedback signal

- (5) Filter current which flows between primary and secondary via the Y-Capacitor.

#### Points in pattern designing

- · GND wiring of the above 1)-5) should be separated so as not to affect each other.

- To minimize the surge voltage of MOSFET, loop length of the main circuit should be design as short as possible.

- $\cdot\,$  The electrolytic capacitor between VCC pin and GND should be connect close to the IC.

- $\cdot\,$  The bypass capacitor of the VCC pin should be connect as close as possible to the IC.

- $\cdot$  Capacitors for filter such as FB pin and CS pin should be connect close to each pin using the shortest wiring.

- $\cdot\,$  The loop area of CS pin and GND wiring should be as small as possible.

- · The current sense resistor and electrolytic capacitor should be connect as short as possible.

- $\cdot\,$  The IC and control circuit should not be arranged within the main circuit loop.

- · Control circuit and signal wiring should not be placed under the transformer so as not to affect the leakage flux.

#### **12. Application circuit example**

The typical application circuit shown here provides specifications common to each IC series.

Note) This application circuit is a reference material for describing typical usage of this IC, and does not guarantee the operation or characteristics of the IC.

| Caut | ion |

|------|-----|

|------|-----|

| 1. | The contents of this note (Product Specification, Characteristics, Data, Materials, and Structure etc.) were prepared in |

|----|--------------------------------------------------------------------------------------------------------------------------|

|    | December 2012. The contents will subject to change without notice due to product specification change or some other      |

|    | reasons. In case of using the products stated in this document, the latest product specification shall be provided and   |

|    | the data shall be checked.                                                                                               |

- 2. The application examples in this note show the typical examples of using Fuji products and this note shall neither assure to enforce the industrial property including some other rights nor grant the license.

- 3. Fuji Electric Co.,Ltd. is always enhancing the product quality and reliability. However, semiconductor products may get out of order in a certain probability. Measures for ensuring safety, such as redundant design, spreading fire protection design, malfunction protection design shall be taken, so that Fuji Electric semiconductor product may not cause physical injury, property damage by fire and social damage as a result.

- 4. Products described in this note are manufactured and intended to be used in the following electronic devices and electric devices in which ordinary reliability is required:

- Computer OA equipment Communication equipment (Pin) Measuring equipment

- Machine tool Audio Visual equipment Home appliance Personal equipment

- Industrial robot etc.

- 5. Customers who are going to use our products in the following high reliable equipments shall contact us surely and obtain our consent in advance. In case when our products are used in the following equipment, suitable measures for keeping safety such as a back-up-system for malfunction of the equipment shall be taken even if Fuji Electric semiconductor products break down:

- Transportation equipment (in-vehicle, in-ship etc.) Communication equipment for trunk line

- Traffic signal equipment Gas leak detector and gas shutoff equipment

- Disaster prevention/Security equipment Various equipment for the safety.

- 6. Products described in this note shall not be used in the following equipments that require extremely high reliability: - Space equipment - Aircraft equipment - Atomic energy control equipment

- Undersea communication equipment Medical equipment.

- 7. When reprinting or copying all or a part of this note, our company's acceptance in writing shall be obtained.

- 8. If obscure parts are found in the contents of this note, contact Fuji Electric Co.,Ltd. or a sales agent before using our products. Fuji Electric Co.,Ltd. and its sales agents shall not be liable for any damage that is caused by a customer who does not follow the instructions in this cautionary statement.

- The contents will subject to change without notice due to product specification change etc.

- Application examples and component in this sheet is for the purpose of assisting in the design. Therefore, This sheet has not been made in consideration of the margin.

- Before using, Please design in consideration of the parts variation and use condition.